ニュース

Intel,エクサスケール計画の現状を報告。東大教授が語る,「エクサスケール実現に向けた意外な壁」とは?

|

内容はバリバリの「企業向け」で,4Gamerの守備範囲からは外れ気味だが,Intelが取り組むメニーコアプロジェクト「MIC」(マイク)の現状が語られたので,要点をかいつまんでレポートしてみたい。

1000人のエンジニアが取り組む

ビッグプロジェクト「MIC」

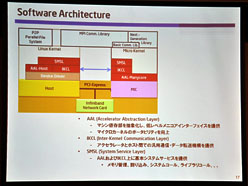

MIC(Many Integrated Core)は,その名のとおり,多数のコアを集積したプロセッサだ。ファミリー名は「Knights」(ナイツ,開発コードネーム)で,HPC(High Performance Computing)向けとされている。

|

これに対して,Knightsファミリーの場合,CPUと同じx86コアを多数集積し,ホストCPUと協調動作して演算性能を引き上げる,ホモジニアスなアーキテクチャになっている。現時点だと,45nmプロセス技術を用いて製造され,32基のx86コアを内蔵した「Kights Ferry」(ナイツフェリー,開発コードネーム)を搭載するPCI Express x16カードが開発者に配布されており,各所で研究開発が進められている。

|

憶えている読者も多いと思われるが,Intelが一時期取り組んでいたオリジナルGPU計画「Larrabee」(ララビー)から派生した,というか,Larrabee計画を修正して引き継いだのがKnightsファミリーであり,MIC計画である。

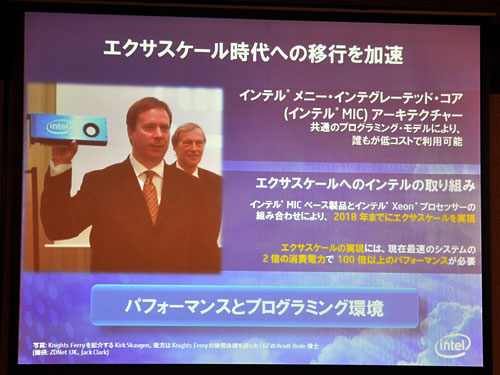

Skaugen氏は,MIC計画の進展について「開発は予定どおり進行中だ。Intelは,このMICアーキテクチャを用いて,2018年までに,エクサスケールのHPCを実現する目標を掲げている」と語る。

|

エクサスケールというのは,1EFLOPS(エクサフロップス,1000PFLOPS=10の18乗FLOPS)の演算性能を持つコンピュータのことだ。4Gamer読者になじみ深いところでは,NVIDIAなどが米国防総省の関連機関から援助を受けてエクサスケールを目指しているのがよく知られるところである。。

これに対しIntelは,日本時間8月30日付けで「Intel Federal」(インテルフェデラル)という子会社を設立。Intel Federalは米国政府機関との協業を目指して設立された会社で,Skaugen氏も「米政府と協業してエクサスケールに取り組んでいく」と述べていた。もっとも,ほかの国に門戸を閉ざしているわけではないそうで「日本などとも協業していていきたい」(同氏)とのことだったが。

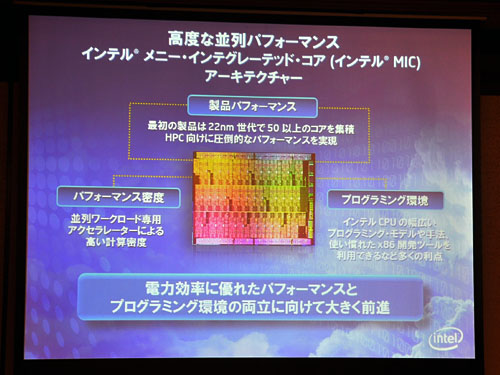

さて,2018年に向けた具体的なロードマップだが,Skaugen氏は,22nmプロセス技術を採用して製造される次世代プロセッサとして6月に概要が発表された「Knights Corner」(ナイツコーナー,開発コードネーム)についても触れ,「50コア以上をCPUと同じプログラミング環境で利用できる」と,アピールしていた。

このKnights Cornerも2018年のエクサスケール実現に向けた通過点にすぎないが,Skaugen氏によると「MIC計画には約1000人のエンジニアが取り組んでいる」そうで,本計画にIntelが本気で取り組んでいることは確かなようだ。

|

エクサスケール到達に立ちはだかる意外な壁

|

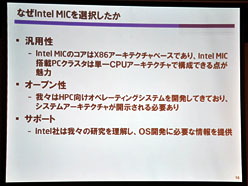

まず石川氏はMICを選んだ理由として「GPUは単独で動かない」ことを挙げていた。GPUはホストCPUがないと機能しないが,x86コアを集積したMICはそうではないというわけだ。また,MICは単一のCPUアーキテクチャで構成され,GPUに比べて汎用性が高いことも利点だという。

|

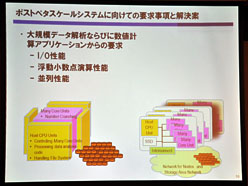

石川氏のグループでは,並列性能の向上とI/O性能の向上を同時に満たすハードウェアやソフトウェアの開発に取り組んでいるという。

|

……というわけで,KnightsファミリやMICアーキテクチャはなかなか興味深いのだが,この技術がコンシューマーに降りてくる予定は今のところない。Larrabee計画の打ち切りから考えても,将来のIntel製統合型グラフィックス機能にこの技術がそのまま採用される可能性は低く,「Knightsファミリー向けに開発されたインターコネクトやベクタ演算周りは応用される可能性があるかな?」という程度だろう。

ただ,業界をあげて取り組んでいるエクサスケールに向け,Intelがどう取り組んでいるのかは,今後のコンピュータ業界を追ううえで,注目しておくと面白そうだ。

→インテル

→Intel Federal設立のニュースリリース(英語)

- 関連タイトル:

Xeon Phi

Xeon Phi - この記事のURL: